I am seeing something across multiple classic Bally pins that makes me think it is an actual bug in the firmware. It has to do with the LATCH signals for the displays. Specifically the Credit/Match/Ball (CMB) display.

Before we go any further, here is a simplified explanation about how the displays are updated by the game. All of the displays share a set of four signals that are used for the BCD data (0-9) for the value to show in a particular digit. They also share another six (or seven) signals that are used to indicate which digit the value is being set for. That brings us to the LATCH signals – each display has its own LATCH signal and they are used so that a display remembers its last set value and continues to show that value as the game goes on to update the next display. Each digit on each display is updated one at a time, but human persistence of vision makes it look like all of the displays’ digits are lit up at the same time.

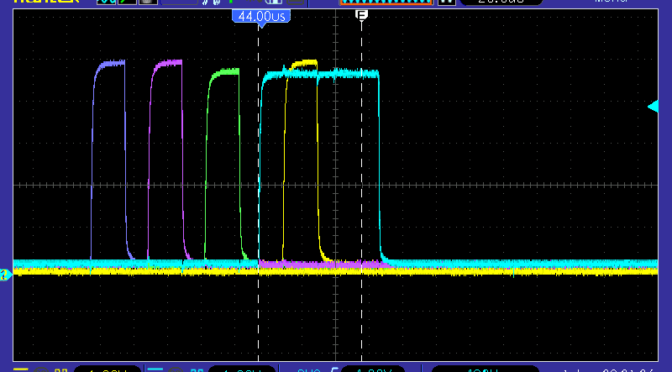

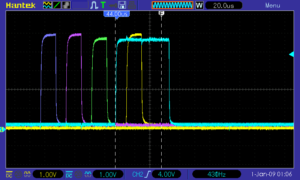

So one would expect a nice, orderly, consistent signaling where one display’s digit-value is set, then the next one, then the next one, and so on. But what we get this is:

What you see above is a combined image of all of the LATCH signals. I scoped out the different player displays’ LATCH signals against the LATCH signal for the CMB display, then overlaid themselves together and used different colors to differentiate the different signals. (Yeah, I know I have to re-comp the probes a bit…)

Going from left to right the shorter duration signals are for displays 1-4 (Player 1, Player 2, Player 3, and Player 4), and the longer one is for display 5 (CMB). Given what the LATCH signal is used for, one can see that this could be an issue. But the latches used by the displays are transparent latches. The displays do not “snapshot” and store the data that is present when the LATCH signal is asserted. Instead, data that is present passes through the latch whilst the signal is asserted and then when the signal is de-asserted, the data currently present is stored by the latches.

That behavior is what allows the CMB display to correctly show its own data instead of the data from one of the other displays. Even if another display’s data is placed on the shared lines while the CMB’s LATCH signal is asserted, it will not be “remembered” by the CMB display because nothing is stored by it until its own LATCH signal is de-asserted.

So even though it looks like the behavior of the LATCH signals appear to be somewhat buggy, the average person never even knows because of how the hardware behaves.

It might be interesting to see if Stern pins of the same era also have the same bug. They copied the hardware for the most part (MPU, displays, etc.), I wonder if they went a little too far with what they copied…